### **Dual Monolithic Tone Decoder**

#### **GENERAL DESCRIPTION**

The XR-2567 is a dual monolithic tone decoder of the 567-type that is ideally suited for tone or frequency decoding in multiple-tone communication systems. Each decoder of the XR-2567 can be used independently or both sections can be interconnected for dual operation. The matching and temperature tracking characteristics between decoders on this monolithic chip are superior to those available from two separate tone decoder coder packages.

The XR-2567 operates over a frequency range of 0.01 Hz to 500 kHz. Supply voltages can vary from 4.5V to 12V, with internal voltage regulation provided for supplies between 7V and 12V. Each decoder consists of a phase-locked loop (PLL), a quadrature AM detector, a voltage comparator, and a logic compatible output that can sink more than 100 mA of load current.

The center frequency of each decoder is set by an external resistor and capacitor which determine the freerunning frequency of each PLL. When an input tone is present within the passband of the circuit, the PLL "locks" on the input signal. The logic output, which is normally "high", then switches to a "low" state during this "lock" condition.

#### FEATURES

Replaces two 567-type decoders Excellent temperature tracking between decoders Bandwidth adjustable from 0 to 14% Logic compatible outputs with 100 mA sink capability Center frequency matching (1% typ.) Center frequency adjustable from 0.01 Hz to 500 kHz Inherent immunity to false triggering Frequency range adjustable over 20:1 range by

external resistor.

#### APPLICATIONS

| Touch-Tone® Decoding<br>Sequential Tone Decoding | Full-Duplex Carrier-Tone<br>Transceiver |

|--------------------------------------------------|-----------------------------------------|

| Dual-Tone Decoding/                              | Wireless Intercom                       |

| Encoding                                         | Dual Precision                          |

| Communications Paging                            | Oscillator                              |

| Ultrasonic Remote-                               | FSK Generation and                      |

| Control and Monitoring                           | Detection                               |

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply                      |              |

|-----------------------------------|--------------|

| With Internal Regulator           | 14V          |

| Without Regulator (Pins 12 and 13 | shorted) 10V |

| Power Dissipation                 |              |

| Ceramic Package                   | 750 mW       |

| Derate Above +25°C                | 6 mW/°C      |

| Plastic Package                   | 625 mW/°C    |

| Derate Above +25°C                | 5.5 mW/°C    |

|                                   |              |

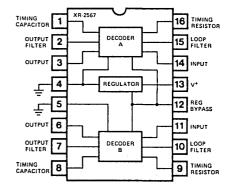

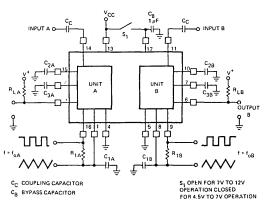

#### FUNCTIONAL BLOCK DIAGRAM

Operating Temperature XR-2567M XR-2567C Storage Temperature

- 55°C to + 125°C 0°C to + 70°C - 65°C to + 150°C

#### **ORDERING INFORMATION**

| Part Number | Package | Temperature Range |

|-------------|---------|-------------------|

| XR-2567CN   | Ceramic | 0°C to +70°C      |

| XR-2567CP   | Plastic | 0°C to +70°C      |

#### SYSTEM DESCRIPTION

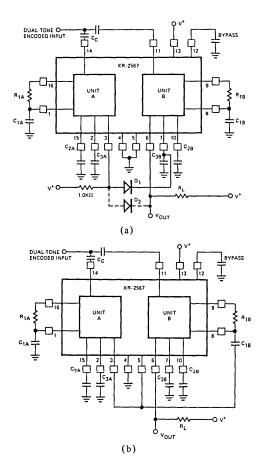

The XR-2567 dual monolithic tone decoder consists of two independant 567-type circuits and an on board voltage regulator. Each decoder has a phase detector, low pass filter, and current controlled oscillator which comprise the basic phase locked loop, plus an additional low pass filter and quadrature detector enabling detection of in-band signals. Both devices have normally high open collector outputs capable of sinking 100 mA.

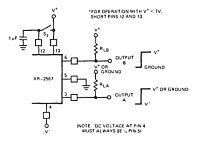

The input signal is applied to Pin 14 (device A) or Pin 11 (device B), both with 20 k $\Omega$  nominal input resistance. Free running frequency is controlled by an RC network at Pins 1 and 16 (device A) or Pins 8 and 9 (device B). A capacitor on Pin 2 (A), or Pin 7 (B) serves as the output filter and eliminates out-of-band triggering. PLL filtering is accomplished with a capacitor on Pin 15 (A), or Pin 10 (B); bandwidth and skew are also dependant upon the circuitry here. Bandwidth is adjustable from 0% to 14% of the center frequency. Pin 13 is +V<sub>CC</sub> (4.75 to 12V nominal, 14V maximum); Pin 7 is ground; and Pin 3 (A) or Pin 6 (B) is the open collector output, pulling low when an in-band signal triggers the device.

Voltage supplies below 7V necessitate bypassing the internal regulator. This is accomplished by shorting Pin 12 to V<sub>CC</sub>; for supplies over 7V, a bypass capacitor of at least 1  $\mu$ F should AC ground Pin 12.

6-115

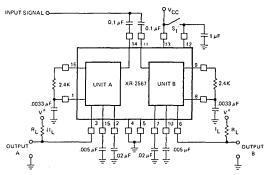

**ELECTRICAL CHARACTERISTICS** Test Conditions:  $V_{CC} = +5V$ ,  $T_A = 25^{\circ}$  C, unless otherwise specified. Test circuit of Figure 2, S<sub>1</sub> closed unless otherwise specified.

|                                                                                                                                                                                                                                                                   | LIMITS      |                                                       |                                               |                                                         |                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                        | MIN         | ТҮР                                                   | MAX                                           | UNITS                                                   | CONDITIONS                                                                                                                                                                            |

| GENERAL<br>Supply Voltage Range<br>Without Regulator<br>With Internal Regulator<br>Supply Current (both decoders)<br>Quiescent XR-2567M<br>XR-2567C<br>Activated XR-2567M<br>XR-2567C<br>Output Voltage<br>Negative Voltage at Input<br>Positive Voltage at Input | 4.75<br>6.5 | 12<br>14<br>22<br>24                                  | 7<br>12<br>16<br>20<br>26<br>30<br>15<br>- 10 | Vdc<br>Vdc<br>mA<br>mA<br>MA<br>V<br>V<br>V             | See Figure 5, S <sub>1</sub> closed.<br>See Figure 5, S <sub>1</sub> open.<br>See Figure 7, 8<br>$R_L = 20 k\Omega$<br>$R_L = 20 k\Omega$<br>$R_L = 20 k\Omega$<br>$R_L = 20 k\Omega$ |

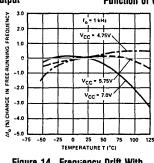

| Centrer FREQUENCY (each decoder section)<br>Highest Center Frequency<br>Center Frequency Stability<br>Temperature $T_A = 25^{\circ}C$<br>$0^{\circ} < T_A < + 70^{\circ}C$<br>$-55^{\circ} < T_A < + 125^{\circ}C$<br>Supply Voltage                              | 100         | 500<br>35<br>±60<br>±140                              | V <sub>CC</sub> +0.5                          | kHz<br>ppm/°C<br>ppm/°C<br>ppm/°C                       | See Figure 14<br>See Figure 14<br>See Figure 14                                                                                                                                       |

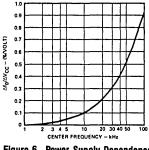

| Without Regulator<br>XR-2567M<br>XR-2567C<br>With Internal Regulator<br>XR-2567M<br>XR-2567C                                                                                                                                                                      |             | 0.5<br>0.7<br>0.05<br>0.1                             | 1.0<br>2.0                                    | % /V<br>% /V<br>% /V<br>% /V                            | $f_{0} = 100 \text{ kHz}$<br>$f_{0} = 100 \text{ kHz}$<br>$f_{0} = 100 \text{ kHz}, V_{CC} = 9V$<br>$f_{0} = 100 \text{ kHz}, V_{CC} = 9V$                                            |

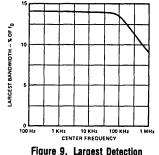

| DETECTION BANDWIDTH<br>(each decoder section)<br>Largest Detection Bandwidth<br>XR-2567M<br>XR-2567C<br>Largest Detection Bandwidth Skew<br>XR-2567M<br>XR-2567C<br>Largest Detection Bandwidth Variation<br>Temperature<br>Supply Voltage                        | 12<br>10    | 14<br>14<br>1<br>±0.1<br>±2                           | 16<br>18<br>2<br>3                            | % of fo<br>% of fo<br>% of fo<br>% of fo<br>%/°C<br>%/V | $f_0 = 100 \text{ kHz}$<br>$f_0 = 100 \text{ kHz}$<br>$V_{in} = 300 \text{ mV rms}$<br>$V_{in} = 300 \text{ mV rms}$                                                                  |

| INPUT (each decoder section)<br>Input Resistance<br>Smallest Detectable Input Voltage<br>Largest No-Output Input Voltage<br>Greatest Simultaneous Outband<br>Signal to Inband Signal Ratio<br>Minimum Input Signal to Wideband<br>Noise Ratio                     | 10          | 20<br>20<br>15<br>+6<br>-6                            | 25                                            | kΩ<br>mV rms<br>mV rms<br>dB<br>dB                      | $I_L = 100 \text{ mA}, f_i = f_0$<br>$I_L = 100 \text{ mA}, f_i = f_0$<br>Noise BW = 140 kHz                                                                                          |

| OUTPUT (each decoder section)<br>Output Saturation Voltage<br>Output Leakage Current<br>Fastest ON-OFF Cycling Rate<br>Output Rise Time<br>Output Fall Time                                                                                                       |             | 0.2<br>0.6<br>0.01<br>f <sub>0</sub> /20<br>150<br>30 | 0.4<br>1.0<br>25                              | V<br>V<br>μA<br>ns                                      | $I_{L} = 30 \text{ mA}, V_{in} = 25 \text{ mV rms}$ $I_{L} = 100 \text{ mA}, V_{in} = 25 \text{ mV rms}$ $R_{L} = 50\Omega$ $R_{L} = 50\Omega$                                        |

| MATCHING CHARACTERISTICS<br>Center Frequency Matching<br>Temperature Drift Matching                                                                                                                                                                               |             | 1<br>±20<br>±50                                       |                                               | %<br>ppm/°C<br>ppm/°C                                   | f <sub>o</sub> = 10 kHz<br>0°C <t<sub>A&lt;70°C<br/>−55°C<t<sub>A&lt;125°C</t<sub></t<sub>                                                                                            |

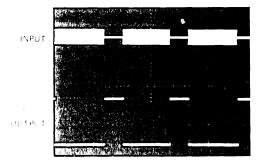

Response to 100 mV rms tone burst.  $R_{L} = 100$  ohms.

#### **DEFINITIONS OF XR-2567 PARAMETERS**

$f_0$  is the *free-running frequency* of the currentcontrolled oscillator of the PLL with no input signal. It is determined by resistor  $R_1$  and capacitor  $C_1$ ;  $f_0$  can be approximated by

$$f_0 \approx \frac{1}{R_1C_1} Hz$$

where  $R_1$  is in ohms and  $C_1$  is in farads.

The detection bandwidth is the frequency range centered about  $f_0$ , within which an input signal larger than the threshold voltage (typically 20 mV rms) will cause a "logic zero" state at the output. The detection bandwidth corresponds to the capture range of the PLL and is determined by the low-pass bandwidth filter. The bandwidth of the filter, as a percent of  $f_0$ , can be determined by the approximation

BW

$$\approx 1070 \sqrt{\frac{V_i}{f_0 C_2}}$$

where V<sub>i</sub> is the input signal in volts, rms, and C<sub>2</sub> is the capacitance in  $\mu$ F at Pins 10 or 15.

The largest detection bandwidth is the largest frequency range within which an input signal above the threshold voltage will cause a logical zero state at the output. The maximum detection bandwidth corresponds to the lock range of the PLL.

The detection band skew is a measure of how accurately the largest detection band is centered about the center frequency,  $f_0$ . It is defined as ( $f_{max} + f_{min} - 2f_0$ )/ $f_0$ , where  $f_{max}$  and  $f_{min}$  are the frequencies corresponding to the edges of the detection band. If necessary, the detection band skew can be reduced to zero by an optional centering adjustment. (See Optional Controls.)

#### DESCRIPTION OF CIRCUIT CONTROLS

#### INPUT (Pins 11 and 14)

The input signal is applied to Pins 14 and/or 11 through a coupling capacitor, C<sub>C</sub>. These terminals are internally biased at a dc level 2 volts above ground and they have an input impedance level of approximately 20 k $\Omega$ .

### TIMING RESISTOR $R_1$ AND CAPACITOR $C_1$ (Pins 1, 8, 9, and 16)

The center frequency,  $f_0$ , of each decoder section is set by a resistor  $R_1$  and a capacitor  $C_1.\ R_{1A}$  is connected between Pins 1 and 16 in decoder section A, and  $R_{1B}$  between Pins 8 and 9 of decoder section B.  $C_{1A}$  is connected from Pin 1 to ground, and  $C_{1B}$  from Pin 8 to ground, as shown in Figure 4.  $R_1$  and  $C_1$  should be selected for the desired center frequency by the expression  $f_0\approx 1/R_1C_1$ . For optimum temperature stability,  $R_1$  should be selected such that 2 k $\Omega \leq R_1 \leq 20 \ k\Omega$ , and the  $R_1C_1$  product should have sufficient stability over the projected operating temperature range.

Figure 4. Circuit Connection Diagram

For decoder section A, the oscillator output can be obtained at either Pin 1 or 16. Pin 16 is the oscillator squarewave output which has a magnitude of approximately  $V_{CC} - 1.4V$  and an average dc level of  $V_{CC}/2$ . A 1 k $\Omega$  load may be driven from this point. The voltage at

#### **TYPICAL CHARACTERISTICS**

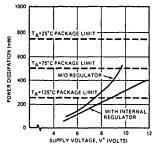

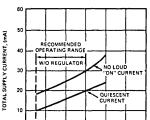

Figure 5. Internal Power Dissipation vs. Supply Voltage. Both Units Activated,  $R_L = 20 k$

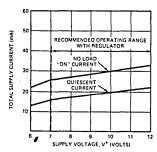

Figure 8. Total Supply Current vs. Supply Voltage for Operation with Internal Regulator (Pins 12 and 13 Not Connected)

Figure 11. Greatest Number of **Cycles Before Output**

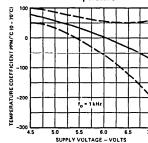

Figure 14. Frequency Drift With Temperature

Figure 6. Power Supply Dependence of Center Frequency

Bandwidth

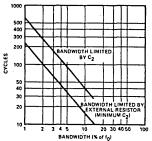

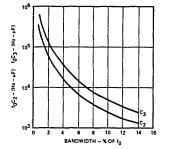

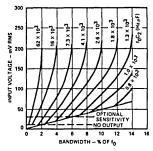

Figure 12. Detection Bandwidth as a Function of C2 and C3

Figure 15. Temperature Coefficient of Center Frequency (Mean and S.D.)

Figure 7. Total Supply Current vs. Supply Voltage for Operation Without Internal Regulator (Pins 12 and 13 Shorted)

LY VOLTAGE, V

8 9 10

(VOLTS)

6

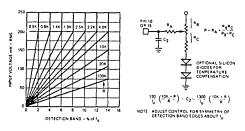

Figure 10. Bandwidth vs. Input Signal Amplitude (C<sub>2</sub> in  $\mu$ F)

Figure 13. Bandwidth Variation With Temperature

XR-2567

6-118

pin 1 is an exponential triangle waveform with a peakto-peak amplitude of 1 volt and an average dc level of  $V_{CC}/2$ . Only high impedance loads should be connected to Pin 1 to avoid disturbing the temperature stability or duty cycle of the oscillator. For section B, Pin 9 is the squarewave output and Pin 8 the exponential triangle waveform output.

#### LOOP FILTER, C<sub>2</sub> (Pins 10 and 15)

Capacitors C2A and C2B connected from Pins 15 and 10 to ground are the single-pole, low-pass filters for the PLL portion of decoder sections A and B. The filter time constant is given by  $T_2 = R_2C_2$ , where  $R_2$  (10 k $\Omega$ ) is the impedance at Pins 10 or 15. The selection of C<sub>2</sub> is determined by the detection bandwidth requirements and input signal amplitude as shown in Figures 10 and 12. One approach is to select an area of operation from the graph and then adjust the input level and value of C<sub>2</sub> accordingly. Or, if the input amplitude variation is known, the required  $f_0C_2$  product can be found to give the desired bandwidth. Constant bandwidth operation requires  $V_i > 200 \text{ mV rms}$ . Then, as noted in Figure 10, bandwidth will be controlled solely by the foC2 product. (For additional information, see Optional Controls Section, "Speed of Response" and "Bandwidth Reduction".)

Pins 10 and 15 correspond to the PLL phase detector outputs of sections A and B, respectively. The voltage level at these pins is a linear function of frequency over the range of 0.95 to 1.05  $f_0$ , with a slope of approximately 20 mV/% frequency deviation.

#### OUTPUT FILTER, C3 (Pins 2 and 7)

Capacitors C<sub>3A</sub> and C<sub>3B</sub> connected from Pins 2 and 7 to ground form low-pass post detection filters for sections A and B respectively. The function of the post detection filter is to eliminate spurious outputs caused by out-of-band signals. The time constant of the filter can be expressed as  $T_3 = R_3C_3$ , where  $R_3$  (4.7 k) is the internal impedance at Pins 2 or 7.

The precise value of  $C_3$  is not critical for most applications. To eliminate the possibility of false triggering by spurious signals, a minimum value for  $C_3$  is  $2C_2$ , where  $C_2$  is the loop filter capacitance for the corresponding decoder section. If  $C_3$  is smaller than  $2C_2$ , then frequencies adjacent to the detection band may switch the output stage "off" and "on" at the beat frequency, or the output may pulse "off" and "on" during the turnon transient.

If the value of  $C_3$  becomes too large, the turn-on or turn-off time of the output stage will be delayed until the voltage change across  $C_3$  reaches the threshold voltage. In certain applications, this delay may be desirable as a means of suppressing spurious outputs. (For additional information, see Optional Controls Section, "Speed of Response" and "Chatter".)

#### LOGIC OUTPUT (Pins 3 and 6)

Output terminals 3 and 6 provide a binary logic output when an input signal tone is present within the detection-band of each respective decoder section. The logic outputs are uncommitted "bare-collector" power transistors capable of switching high current loads. The current level at the output is determined by an external load resistor,  $R_L$ , connected from V<sub>CC</sub> to Pins 3 or 6.

When an in-band signal is present, the output transistor at Pins 3 or 6 saturates with a collector voltage less than 1 volt (typically 0.6V) at full rated current of 100 mA. If large output voltage swings are needed, R<sub>L</sub> can be connected to a supply voltage, V + higher than the V<sub>CC</sub> supply. For safe operation, V +  $\leq$  15 volts.

#### **REGULATOR BY-PASS (Pin 12)**

This pin corresponds to the output of the voltage regulator section. For circuit operation with a supply voltage greater than 7V, Pin 12 should be ac grounded with a bypass capacitor  $\geq$  1  $\mu F$ . For circuit operation over a supply voltage range of 4.5 to 7V, the voltage regulator section is not required; Pin 12 should be shorted to V<sub>CC</sub>.

#### **GROUND TERMINALS (Pins 4 and 5)**

To eliminate parasitic interaction, each decoder section has a separate ground terminal. The internal regulator shares a common ground with decoder section A (Pin 4).

Independent ground terminals also allow additional flexibility for split supply operation. Pin 4 can be used as V-, and Pin 5 as ground, as shown in Figure 16. When the circuit is operated with split supplies, the positive supply should always be > 6V, and the dc potential across Pins 13 and 14 should not exceed 15 volts.

Figure 16. Split-Supply Operation Using Independent Ground Terminals of Units A and B. Unit A Operates Between V<sup>+</sup> and V<sup>-</sup>; Unit B Operates Between V<sup>+</sup> and Ground

#### **OPTIONAL CONTROLS**

#### SPEED OF RESPONSE

The minimum lock-up time is inversely related to the loop frequency. As the natural loop frequency is lowered, the turn-on transient becomes greater. Thus, maximum operating speed is obtained when the value of capacitor  $C_2$  is minimum. At the instant an input signal is applied, its phase may drive the oscillator away from the incoming frequency rather than toward it. Under this condition, the lock-up transient is in a worst case situation, and the minimum theoretical lock-up time will not be achievable.

The following expressions yield the values of C<sub>2</sub> and C<sub>3</sub>, in microfarads, which allow the maximum operating speeds for various center frequencies. The minimum rate that digital information may be detected without losing information due to turn-on transient or output chatter is about 10 cycles/bit, which corresponds to an information transfer rate of  $f_0/10$  baud.

$$C_2 = \frac{130}{f_0}, C_3 = \frac{260}{f_0}$$

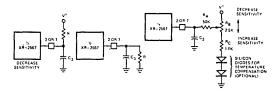

In situations where minimum turn-off time is of less importance than fast turn-on, the optional sensitivity adjustment circuit of Figure 17 can be used to bring the quiescent  $C_3$  voltage closer to the threshold voltage. Sensitivity to beat frequencies, noise, and extraneous signals, however, will be increased.

Figure 17. Optional Connections for Sensitivity Control

#### CHATTER

When the value of  $C_3$  is small, the lock transient and ac components at the lock detector output may cause the output stage to move through its threshold more than once, resulting in output chatter.

Although some loads, such as lamps and relays will not respond to chatter, "logic" may interpret chatter as a series of output signals. Chatter can be eliminated by feeding a portion of the output back to the input or, by increasing the size of capacitor C<sub>3</sub>. Generally, the feedback method is preferred since keeping C<sub>3</sub> small will enable faster operation. Three alternate schemes for chatter prevention are shown in Figure 18. Generally, it is only necessary to assure that the feedback time constant does not get so large that it prevents operation at the highest anticipated speed.

Figure 18. Methods of Reducing Chatter

#### SKEW ADJUSTMENT

The circuits shown in Figure 19 can be used to change the position of the detection band (capture range) within the largest detection band (or lock range). By moving the detection band to either edge of the lock range, input signal variations will expand the detection band in one direction only. Since R<sub>3</sub> also has a slight effect on the duty cycle, this approach may be useful to obtain a precise duty cycle when the circuit is used as an oscillator.

Figure 19. Connections to Reposition Detection Band

#### OUTPUT LATCHING

After a signal is received, the output of either decoder section can be latched "on" by connecting a 20 k $\Omega$  resistor and diode from the "output" terminal to the "output filter" terminal as shown in Figure 20. The output stage can be unlatched by raising the voltage level at the output filter terminal.

Figure 20. Output Latching

#### **POSITIONING OF DETECTION BANDS**

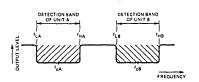

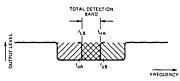

Figure 21 defines the respective band-edge and bandcenter frequencies for sections A and B of the dual tone decoder.

Frequencies  $f_L$  and  $F_H$  with appropriate subscripts refer to the low and the high band-edge frequencies for decoder sections A and B, and  $f_O$  is the center frequency.

(a) Independent Detection of Two Separate Tones

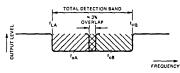

(b) Addition of Detection Bandwidth for Wide-Band Detection

(c) Subtraction of Bandwidths for Narrow-Band Detection

Figure 21. Positioning of Detection Bands

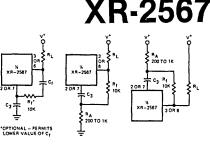

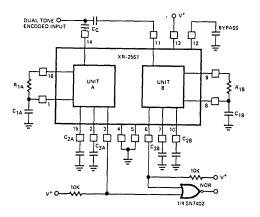

The two sections can be interconnected to form a single tone detector with an overall detection bandwidth equal to the sum or the difference of the detection bands for the two individual detector sections. For example, if the individual decoder sections are interconnected as shown in Figure 25, then the total detection bandwidth would be approximately equal to the sum of the respective bandwidths as shown in Figure 21(b). Similarly, if the decoders are interconnected as shown in Figure 23, then the overall detection band would be equal to the difference, or the overlap, between the respective bandwidths as shown in Figure 21(c).

#### BANDWIDTH REDUCTION

The bandwidth of each decoder can be reduced by either increasing the loop filter capacitor  $C_2$  or reducing the loop gain. Increasing  $C_2$  may be an undesirable solution since this will also reduce the damping of the loop and thus slow the circuit response time.

Figure 22 shows the proper method of reducing the loop gain for reduced bandwidth. This technique will improve damping and permit faster performance under narrow band operation. Bandwidth reduction can also be obtained by subtracting overlapping bandwidths of the two decoder sections (see Figures 21(c) and 23).

Figure 22. Bandwidth Reduction

### APPLICATIONS

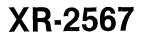

#### **DUAL-TONE DETECTION**

In most dual-tone detection systems, the decoder output is required to change state only when *both* input tones are present simultaneously. This can be implemented by setting the detection bandwidth of each of the XR-2567 decoder sections to cover one of the input tones; and then connecting the respective outputs through a NOR gate, as shown in Figure 23. In this case, the output of the NOR gate will be "high" only when both input tones are present simultaneously.

Figure 24 shows additional circuit configurations which can be used for decoding multiple-tone input signals. In Figure 24(a), the output of Unit A is connected to the output filter (Pin 7) of Unit B through the diode D<sub>1</sub>. *If no input tone is present within the detection-band of Unit* A, then its output (pin 3) is "high", which keeps diode D<sub>1</sub> conducting and "disables" Unit B by keeping its output (pin 6) "high". *If an input tone is present within the detection-band of Unit* A, Pin 3 is low, diode D<sub>1</sub> is reverse biased, and decoder B is no longer disabled. If under these conditions an input signal is present within the detection-band of Unit B, then its output at Pin 6 would be "low". Thus, the output at Pin 6 is "low" only

when input tones within the detection-band of A and B are present simultaneously.

The dual-tone decoder circuit of Figure 24(b) makes use of the split-ground feature of the XR-2567. The output terminal of Unit A is used as a "switch" in series with the ground terminal (Pin 5) of Unit B. If the input tone A is not present, Pin 3 is at its high-impedance state, and the ground terminal of Unit B is opencircuited. When the input tone A is present, Pin 3 goes to a low-impedance state and Unit B is activated. In this manner, the output of Unit B will be "low" only when both tones A and B are present.

In the circuit connection of Figure 24(b), Unit B does not draw any current until it is activated. Therefore, its power dissipation in a stand-by condition is lower than other dual-tone decoder configurations. However, due to finite series resistance between Pin 3 and ground when Unit B is activated, the output current sink capability is limited to  $\leq$  10 mA.

Figure 24. Additional Dual-Tone Decoding Circuits

#### SEQUENTIAL TONE DECODING

Dual-tone decoder circuits can also be used for sequential tone decoding where one tone must be present before the other for the circuit to operate. This can be achieved by making the output filter capacitance,  $C_3$ , of one of the sections large with respect to the other. For example, in the circuits of Figures 24(a) and 24(b), if  $C_{3A}$  is chosen to be much larger than  $C_{3B}$  ( $C_{3A} \ge$  $C_{3B}$ ), then Unit A will remain "on" and activate B for a finite time duration after tone A is terminated. Thus, the circuit will be able to detect the two tones only if they are present sequentially, with tone A preceding tone B.

The circuit of Figure 24(a) can also be modified for sequential tone decoding by addition of a diode,  $D_2$ , between pins 3 and 6. Once activated by Unit A, Unit B will stay "on" as long as tone B is present, even though tone A may terminate. Once tone B disappears, the circuit is reset to its original state and would require tone A to be present for activation.

#### **HIGH-SPEED NARROW-BAND TONE DECODER**

The circuit of Figure 23 can be used as a narrow-band tone decoder by overlapping the detection bands of Units A and B (see Figure 21(c)). The output of the NOR gate will be high only when an input signal is present within the overlapping portions of the detection band. To maintain uniform response within the pass-band, the input signal amplitude should be  $\geq$  80 mV rms. For minimum response time, PPL filter capacitors C<sub>2A</sub> and C<sub>2B</sub> should be:

$$C_{2A} = C_{2B} \cong \frac{130}{f_0 (Hz)} \mu F$$

Under this condition, the worst-case output delay is  $\approx 10$  to 14 cycles of the input tone.

The practical matching and tracking tolerances of individual units limit the minimum bandwidth to  $\approx 4\%$  of f<sub>0</sub>.

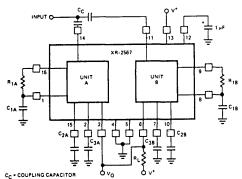

#### WIDE-BAND TONE DECODER

Figure 25 is a circuit configuration for increasing the detection bandwidth of the XR-2567 by combining the respective bandwidths of individual decoder sections. If the detection bands of each section are located adjacent to each other as shown in Figure 21(b), and if the two outputs (pins 3 and 6) are shorted together, then the resulting bandwidth is the sum of individual bandwidth. In this manner, the total detection bandwidth can be increased to 24% of center frequency. To maintain uniform response throughout the pass band, the input signal level should be  $\geq 80$  mV, rms, and the respective pass-bands of each section should have  $\approx 3\%$  overlap at center frequency.

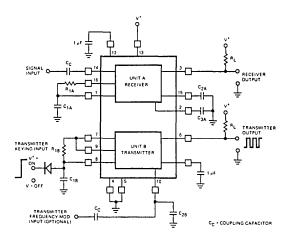

#### TONE TRANSCEIVER

The XR-2567 can be used as a full-duplex tone transceiver by using one section of the unit as a tone detector and the remaining section as a tone generator. Since both sections operate independently, the circuit

Figure 25. Wide-Band Tone Detection

can transmit and receive simultaneously. A recommended circuit connection for transceiver applications is shown in Figure 26. In this case, Unit A is utilized as the receiver, and Unit B is used as the transmitter. The transmitter section can be keyed "on" and "off" by applying a pulse to pin 8 through a disconnect diode D<sub>1</sub>. The oscillator section of Unit B will be keyed "off" when the keying logic level at pin 8 is at a "low" state.

The output of the transmitter section (Unit B) can also be frequency modulated over a +6% deviation range by applying a modulation signal to pin 10.

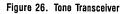

#### HIGH CURRENT OSCILLATOR

The oscillator output of each section of XR-2567 can be amplified using the high current logic driver sections of the circuit. In this manner, each section of the circuit can switch 100 mA loads, without sacrificing oscillator stability. A recommended circuit connection for this application is shown in Figure 27. The oscillator frequency can be modulated over  $\pm 6\%$  of f<sub>0</sub> by applying a control voltage to pins 15 or 10.